# Shift Registers

Digital Registers- Flip-flop is a 1 bit memory cell which can be used for storing the digital data (either a logic "0" or a "1"). To increase the storage capacity in terms of number of bits, we have to use a group of flip-flop. Such a group of flip-flop is known as a Register. The n-bit register will consist of n number of flip-flop and it is capable of storing an n-bit word. (Flip-flop एक 1 बिट memory cell है जिसका उपयोग डिजिटल डेटा को स्टोर करने के लिए किया जा सकता है। बिट की संख्या के terms में storage capacity बढ़ाने के लिए, हम फ्लिप-फ्लॉप के एक समूह का उपयोग करते है। फ्लिप-फ्लॉप के ऐसे समूह को Register कहा जाता है। n-bit रजिस्टर में n number of flip-flop शामिल होते है और यह n-bit word को संग्रहीत करने में सक्षम है)

The binary data in a register can be moved within the register from one flip-flop to another or towards right hand side or towards left hand side. The registers that allow such data transfers are called as shift registers. रजिस्टर में बाइनरी डेटा को एक फिलप-फ्लॉप से दूसरे में रजिस्टर में या right hand side or towards left hand side move किया जा सकता है। ऐसे डेटा ट्रांसफर की अनुमित देने वाले रजिस्टरों को shift registers कहा जाता है।

An 'N' bit shift register contains 'N' flip-flops (एक 'N' बिट शिफ्ट रजिस्टर में 'N' फ्लिप-फ्लॉप होते हैं)

Register is a sequential circuit . Which have memory element (Register एक sequential circuit जिस में memory element होता है )

- When a number of flip flops are connected in series, this arrangement is called a Register .A simple Shift Register can be made using only D-type flip-Flops, one flip-Flop for each data bit. ( जब flip flops series में connected किया जाता है तो इस arrangement को a Register कहा जाता है .एक साधारण

- शिफ्ट रजिस्टर केवल डी-टाइप फ्लिप-फ्लॉप का उपयोग करके बनाया जा सकता है, प्रत्येक डेटा बिट के लिए एक फ्लिप-फ्लॉप का use किया जाता है )

- The output from each flip-Flop is connected to the D input of the flip-flop at its right ( प्रत्येक फ्लिप-फ्लॉप का आउटपुट अपने right फ्लिप-फ्लॉप के D input से जुड़ा हुआ होता है )

- Shift registers hold the data in their memory which is moved or "shifted" to their required positions on each clock pulse. (Shift registers memory में डेटा को hold करता हैं जो प्रत्येक clock pulse पर अपने required positions पर shifted या moved होता है।)

- Each clock pulse shifts the contents of the register one bit position to either the left or the right. (प्रत्येक clock pulse पर रजिस्टर का contents को या तो बाएं या दाएं shifts होती है।)

- The data bits can be loaded one bit at a time in a series input (SI) configuration or be loaded simultaneously in a parallel configuration (PI). ( डेटा बिट्स series input (SI) configuration में एक समय में एक बिट लोड कर सकता है या साथ साथ parallel configuration (PI) भी में लोड कर सकता है )

- Data may be removed from the register one bit at a time for a series output (SO) or removed all at the same time from a parallel output (PO). (series output (SO) में Data एक बार में एक बिट register से हटाया जा सकता है या parallel output (PO) से एक ही समय में सभी Data को हटाया जा सकता है।)

- One application of shift registers is in the conversion of data between serial and parallel, or parallel to serial. ( शिफ्ट रजिस्टरों का एक अनुप्रयोग data के serial and parallel, or parallel to seria में conversion है)

Basically shift registers are of 4 types. They are

- 1- Serial In Serial Out shift register

- 2- Serial In parallel Out shift register

- 3- Parallel In Serial Out shift register

- 4- Parallel In parallel Out shift register

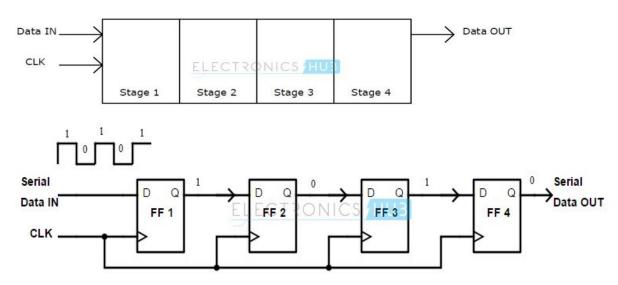

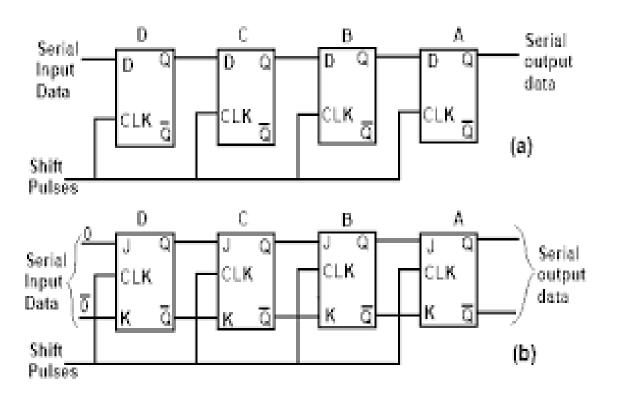

### 1-Serial In Serial Out shift register :-

The shift register, which allows serial input and produces serial output is known as Serial In – Serial Out SISO shift register. The input to this register is given in serial fashion i.e. one bit after the other through a single data line and the output is also collected serially. The data can be shifted only left or shifted only right. Hence it is called Serial in Serial out shift register or a SISO shift register.

As the data is fed from right as bit by bit, the shift register shifts the data bits to left. A 4-bit SISO shift register consists of 4 flip flops .

The registers which will shift the bits to left are called "Shift left registers". The registers which will shift the bits to right are called "Shift right registers."

शिफ्ट रजिस्टर, जो serial input और serial output की अनुमित देता है Serial Out SISO shift register के रूप में जाना जाता है। इस रजिस्टर का इनपुट सीरियल फैशन में दिया गया है यानी single data line के माध्यम से एक के बाद एक बिट दिया जाता है और output भी serially एकत्र किया जाता है। डेटा को only left or only right shifted किया जा सकता है। इसलिए इसे सीरियल आउट शिफ्ट रजिस्टर या SISO शिफ्ट रजिस्टर कहा जाता है।

4-बिट SISO शिफ्ट रजिस्टर में 4 फ्लिप फ्लॉप होते हैं।

जो रजिस्टर बिट्स को बाईं ओर शिफ्ट किया जाएगा उन्हें "शिफ्ट लेफ्ट रजिस्टर" कहा जाता है।

जो रजिस्टर बिट्स को राइट में शिफ्ट करेंगे, उन्हें "Shift राइट रजिस्टर" कहा जाता है।

This one is the simplest register among the four types. the clock signal is connected to all the 4 flip flops. the serial data is connected to the left most or right most flip flop. The output of the first flip flop is connected to the input of the next flip flop and so on. The final output of the shift register is collected at the outmost flip flop.

In this shift register, when the clock signal is applied and the serial data is given; only one bit will be available at output at a time. The use of SISO shift register is to act as temporary data storage device. But the main use of a SISO is to act as a delay element.

यह चार प्रकारों में से सबसे सरल रजिस्टर है। clock signal सभी 4 फिलप फ्लॉप से जुड़ा होता है. serial data सबसे बाईं ओर या सबसे दाईं और के फिलप फ्लॉप connected से होता है। पहले फिलप फ्लॉप का आउटपुट अगले फिलप फ्लॉप और इसी प्रकार अन्य flip flop जुड़े होते है । शिफ्ट रजिस्टर का आउटपुट सबसे अंतिम फिलप फ्लॉप पर से एकत्र किया जाता है।

शिफ्ट रजिस्टर में, जब clock signal applied होता है और serial data टा दिया जाता है तो एक समय में केवल एक बिट आउटपुट पर उपलब्ध होगा। SISO शिफ्ट रजिस्टर का उपयोग अस्थायी डेटा स्टोरेज डिवाइस के रूप में किया है। लेकिन एक SISO का मुख्य उपयोग delay element के रूप में किया जाता है।

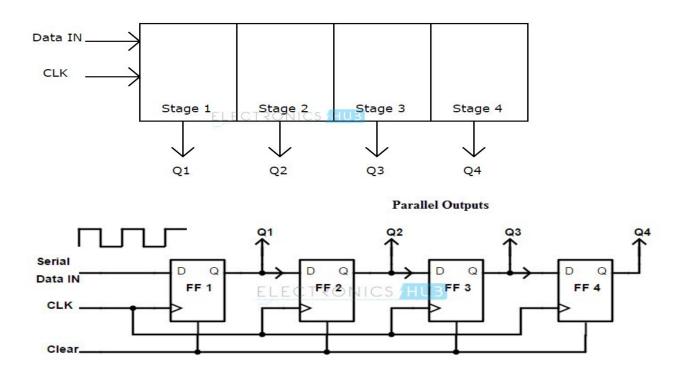

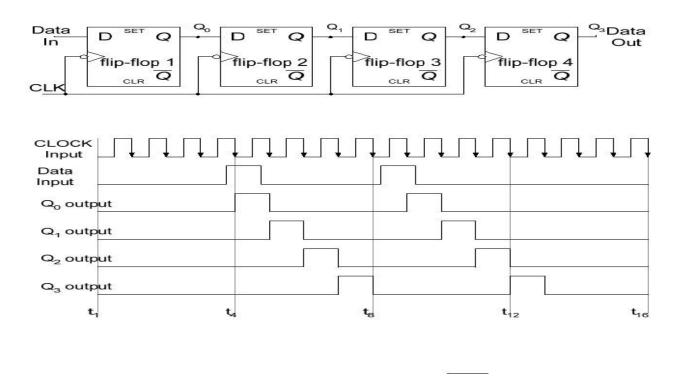

### Serial in Parallel Out shift register:-

The input to this register is given in serial and the output is collected in parallel. या The shift register, which allows serial input and produces parallel output is known as Serial In – Parallel Out SIPO shift register.

The clear (CLR) signal is connected with all the 4 flip flops to RESET the flip flop and the serial data is connected to the flip flop at either end (depending on shift left register or shift right register). The output of the first flip flop is connected to the input of the next flip flop and so on. All the flip flops are connected with a common clock.

clear (CLR) signal फ्लिप फ्लॉप को रीसेट करने के लिए सभी 4 फ्लिप फ्लॉप के साथ जुड़ा हुआ होता है और सीरियल डेटा फ्लिप फ्लॉप के either end से जुड़ा हुआ है यह शिफ्ट लेफ्ट रजिस्टर या शिफ्ट राइट रजिस्टर पर depend होता है . पहले फ्लिप फ्लॉप का आउटपुट अगले फ्लिप फ्लॉप और इसी प्रकार अन्य फ्लिप फ्लॉप कनेक्ट होते है। सभी फ्लिप फ्लॉप common clock के साथ जुड़े हुए होते हैं।

The output of Serial in Parallel out (SIPO) shift register is collected at each flip flop. Q1, Q2, Q3 and Q4 are the outputs of first, second, third and fourth flip flops, respectively. Serial in Parallel out (SIPO) शिफ्ट रजिस्टर में प्रत्येक फिलप फ्लॉप पर output एकत्र किया जाता है। Q1, Q2, Q3 और Q4 क्रमशः पहले, दूसरे, तीसरे और चौथे फिलप फ्लॉप के आउटपुट हैं।

The main application of Serial in Parallel out shift register is to convert serial data into parallel data. Hence they are used in communication lines where demultiplexing of a data line into several parallel line is required.

Serial in Parallel out shift रजिस्टर का मुख्य अनुप्रयोग सीरियल डेटा को समानांतर डेटा में बदलना है। इसलिए उनका उपयोग संचार लाइनों में किया जाता है जहां डेटा लाइन को several parallel line में डिम्टिप्लेक्सिंग की आवश्यकता होती है।

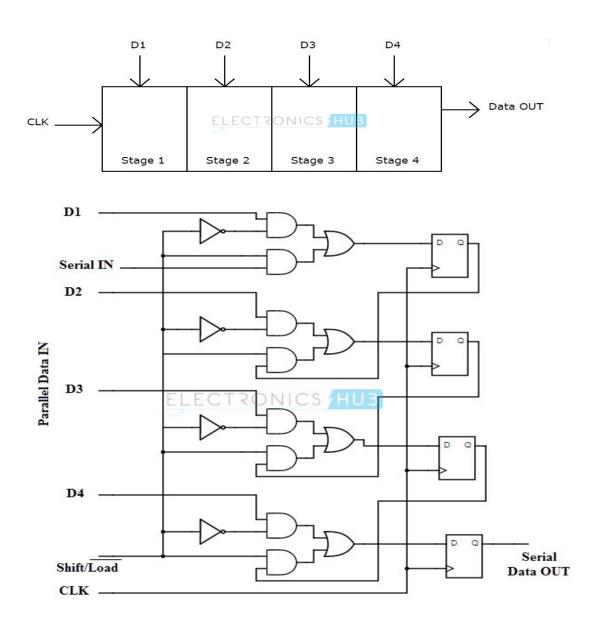

### Parallel in Serial out shift register:-

The input to this register is given in parallel i.e. data is given separately to each flip flop and the output is collected in serial at the output of the end flip flop. (इस रजिस्टर में इनपुट समानांतर में दिया गया है यानी प्रत्येक फ्लिप फ्लॉप के लिए अलग से डेटा दिया जाता है और अंतिम फ्लिप फ्लॉप के आउटपुट से आउटपुट serially एकत्र किया जाता है।)

The clock input is directly connected to all the flip flops and the input data is connected individually to each flip flop through a multiplexer at input of every flip flop. Here D1, D2, D3 and D4 are the individual parallel inputs to the shift register. In this register the output is collected in serial. (क्लॉक इनपुट सभी फ्लिप फ्लॉप से जुड़ा हुआ है और इनपुट डेटा प्रत्येक फ्लिप फ्लॉप के इनपुट पर मल्टीप्लेक्सर से जुड़ा हुआ है। यहां डी 1, डी 2, डी 3 और डी 4 शिफ्ट रजिस्टर में अलग-अलग समानांतर इनपुट हैं। इस रजिस्टर में आउटपुट को सीरियल में एकत्र collected किया जाता है।)

The output of the previous flip flop and parallel data input are connected to the input of the MUX and the output of MUX is connected to the next flip flop.

A Parallel in Serial out (PISO) shift register converts parallel data to serial data. Hence they are used in communication lines where a number of data lines are multiplexed into single serial data line. पिछले फ्लिप फ्लॉप का आउटपुट और समानांतर डेटा इनपुट MUX के इनपुट से जुड़ा होते है और MUX का आउटपुट अगले फ्लिप फ्लॉप से जुड़ा होता है।

Parallel in Serial out (PISO) शिफ्ट रजिस्टर parallel data को serial data में परिवर्तित करता है। इसलिए उनका उपयोग communication lines में किया जाता है जहां number of data lines को single serial data line में multiplexed किया जाता है।

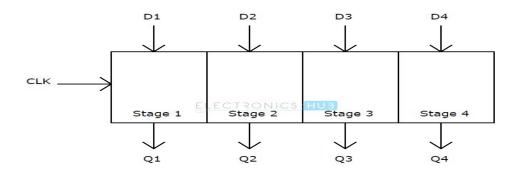

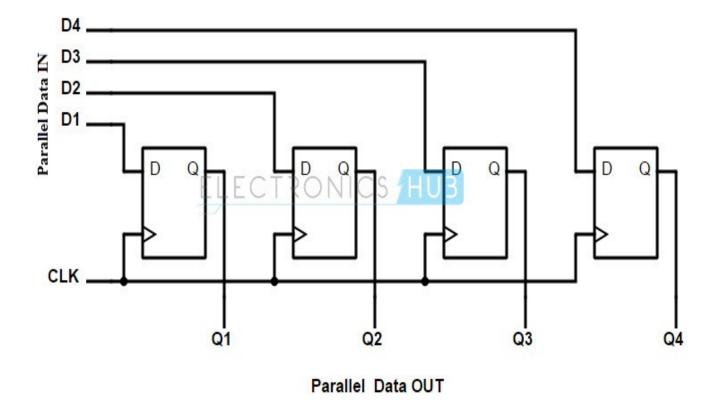

## Parallel in Parallel out shift register:-

In this register, the input is given in parallel and the output also collected in parallel. The clear (CLR) signal and clock signals are connected to all the 4 flip flops. Data is given as input separately for each flip flop and in the same way, output also collected individually from each flip flop.

इस रजिस्टर में, इनपुट समानांतर में दिया जाता है और आउटपुट भी समानांतर में एकत्र किया जाता है।

clear (CLR) signal और clock signals सभी 4 फिलप फ्लॉप से जुड़े हैं। प्रत्येक फिलप फ्लॉप के लिए अलग से इनपुट के रूप में डेटा दिया जाता है और उसी तरह, प्रत्येक फिलप फ्लॉप से आउटप्ट एकत्र किया जाता है।

The above diagram shows the 4 stage parallel in parallel out register. Qa, Qb, Qc and Qd are the parallel outputs and Pa, Pb, Pc and Pd are the individual parallel inputs. There are no interconnections between any of the four flip flops. उपरोक्त आरेख parallel in

parallel out register के 4 चरण को दिखाता है। Qa, Qb, Qc and Qd समानांतर आउटपुट हैं और Pa, Pb, Pc and Pd समानांतर इनपुट हैं। किसी भी चार फ्लिप फ्लॉप के बीच कोई interconnections नहीं हैं।

A Parallel in Parallel out (PIPO) shift register is used as a temporary storage device and also as a delay element similar to a SISO shift register.

Parallel in Parallel out (PIPO) शिफ्ट रजिस्टर का प्रयोग एक temporary storage device के रूप में किया जाता है और SISO शिफ्ट रजिस्टर के समान delay element के रूप में उपयोग किया जाता है।

### **Applications of Shift Registers**

Registers are used in digital electronic devices like computers as

- Temporary data storage

- Data transfer

- Data manipulation

- As counters.

Shift registers are used in computers as memory elements. All the digital systems need to store large amount of data in an efficient manner there we use storage elements like RAM and other type of registers.

Many of the digital system operations like division, multiplication are performed by using registers. The data is transferred through serial shift registers and other type

#### **Delay Line**

Delay line is the most important use of shift registers. A serial in serial out shift register is used to produce time delay, to digital circuits. The time delay can be calculated by using below formula.

$$\Delta t = N * 1 / fc$$

Where N represents number of stages / flip flops and fC represents clock frequency. So an input pulse is delayed by  $\Delta t$  at output. The amount of time delay is controlled flip flops in the shift register or the clock signal frequency.

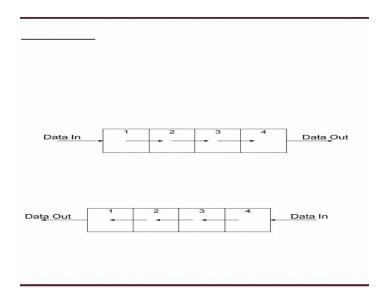

### **Shift Right Operation:-**

Data is shifted in the right-hand direction one bit at a time with each transition of the clock signal. The data enters the shift register serially from the left hand side and after four clock transitions the 4-bit register has 4-bits of data. The data is shifted out serially one bit at a time from the right hand side of the register if clock signals are continuously applied. Thus after 8 clock signals the 4-bit data is completely shifted out of the shift register.

### **Shift Left Out Operation:-**

Data is shifted in the left-hand direction one bit at a time with each transition of the clock signal. The data enters the shift register serially from the right hand side and after four clock transitions the 4-bit register has 4-bits of data. The data is shifted out serially one bit at a time from the left hand side of the register if clock signals are continuously applied. Thus after 8 clock signals the 4-bit data is completely shifted out of the shift register.

शिफ्ट राईट शिफ्ट रजीस्टर

<u>Universal Shift Register :-</u>

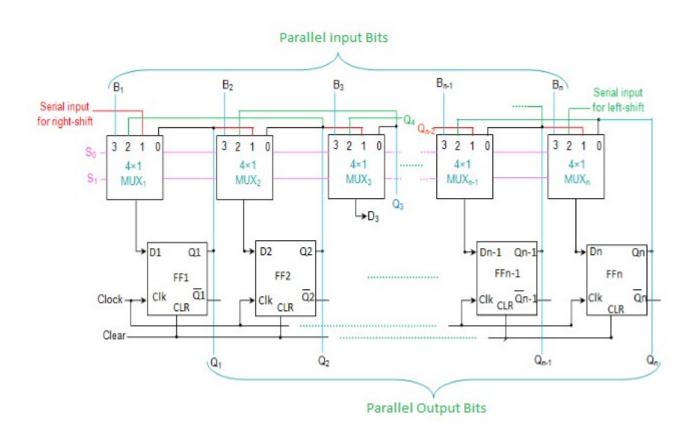

A Universal shift register is a register which has both the right shift and left shift with parallel load capabilities. Universal shift registers are used as memory elements in computers. A Unidirectional shift register is capable of shifting in only one direction. A bidirectional shift register is capable of shifting in both the directions. The Universal shift register is a combination design of bidirectional shift register and a unidirectional shift register with parallel load provision

#### n-bit universal shift register -

A n-bit universal shift register consists of n flip-flops and n 4×1 multiplexers. All the n multiplexers share the same select lines(S1 and S0)to select the mode in which the shift register operates. The select inputs select the suitable input for the flip-flops.

#### Basic connections -

1. The first input (zero th pin of multiplexer) is connected to the output pin of the corresponding flip-flop.

- 2. The second input (first pin of multiplexer) is connected to the output of the very-previous flip flop which facilitates the right shift.

- 3. The third input (second pin of multiplexer) is connected to the output of the verynext flip-flop which facilitates the left shift.

- 4. The fourth input (third pin of multiplexer) is connected to the individual bits of the input data which facilitates parallel loading.

The working of the Universal shift register depends on the inputs given to the select lines.

The register operations performed for the various inputs of select lines are as follows:

| S1 | S0 | REGISTER OPERATION |

|----|----|--------------------|

| 0  | 0  | No changes         |

| 0  | 1  | Shift right        |

| 1  | 0  | Shift left         |

| 1  | 1  | Parallel load      |